Seminar: Reconfigurable Hardware

Contents

Hardware

Coupling

Granularity

- For a 3-bit operation

- 3-bit device will be great

- 8-bit device will have overhead

- For an 8-bit operation

- 3-bit device will be inefficient

- 8-bit device will be great

- For a 3-bit operation

Heterogeneous Arrays

- Base versions of multipliers

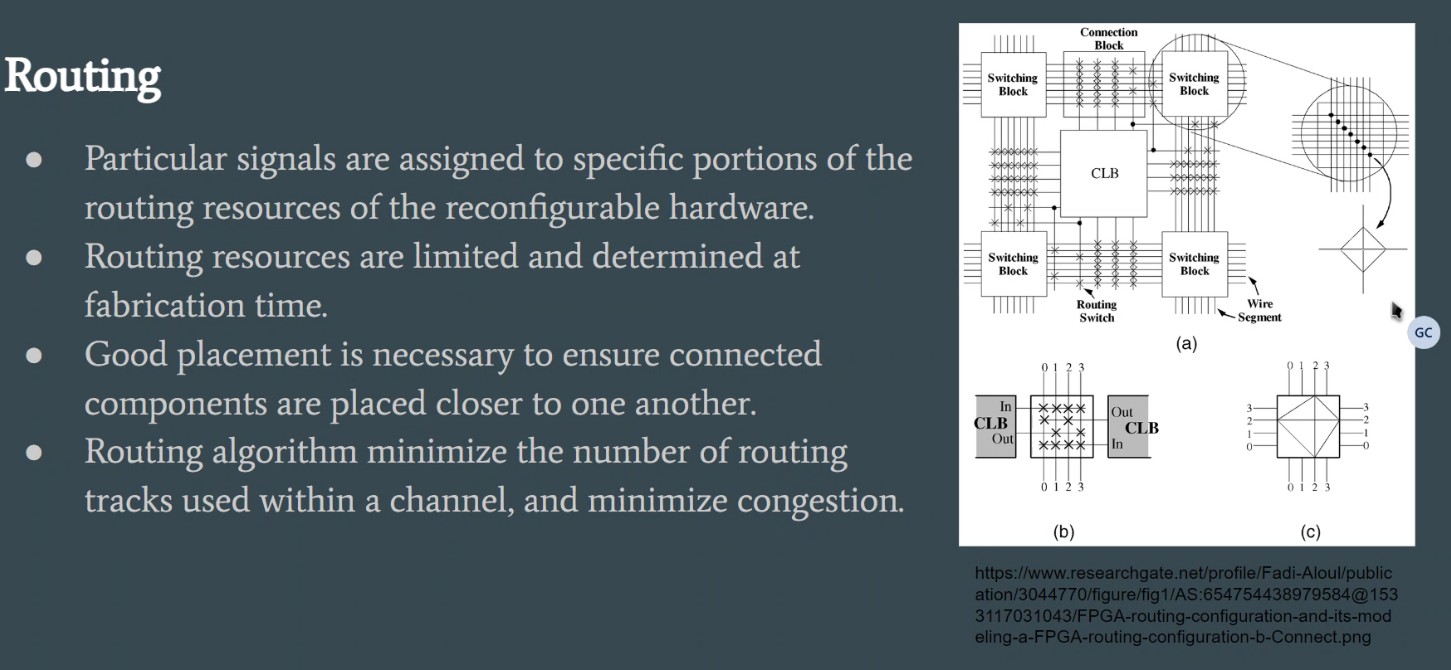

Routing resources

Segmented pathing with switch boxes to emulate longer wires

Hierarchical pathing

Structured dimensions

- One dimension designs are simpler and faster

- Routing abit harder

- Better for simpler connections

- Two dimension designs are more complex (more placement options?

- Routing easier

- One dimension designs are simpler and faster

Multi-FPGA systems

- Mesh - better computation

- Crossbar / SPLASH 2 - better speed

Software

Manual Systems

Yes just design the FPGA chip yourself.

Better precision, but need advanced knowledge

Automated Systems

Eh

Stages

Circuit Specification Stage

Manual

- Hand mapping of the blocks at gate level

Semi-Automated

- Using structural circuit description language

- Generic components

- Requires knowledge of the target

Automated

- Use a high level language (C, C++, Java)

- Specify the logic rather than the block design

Mapping Stage

Placement Stage

Routing Stage

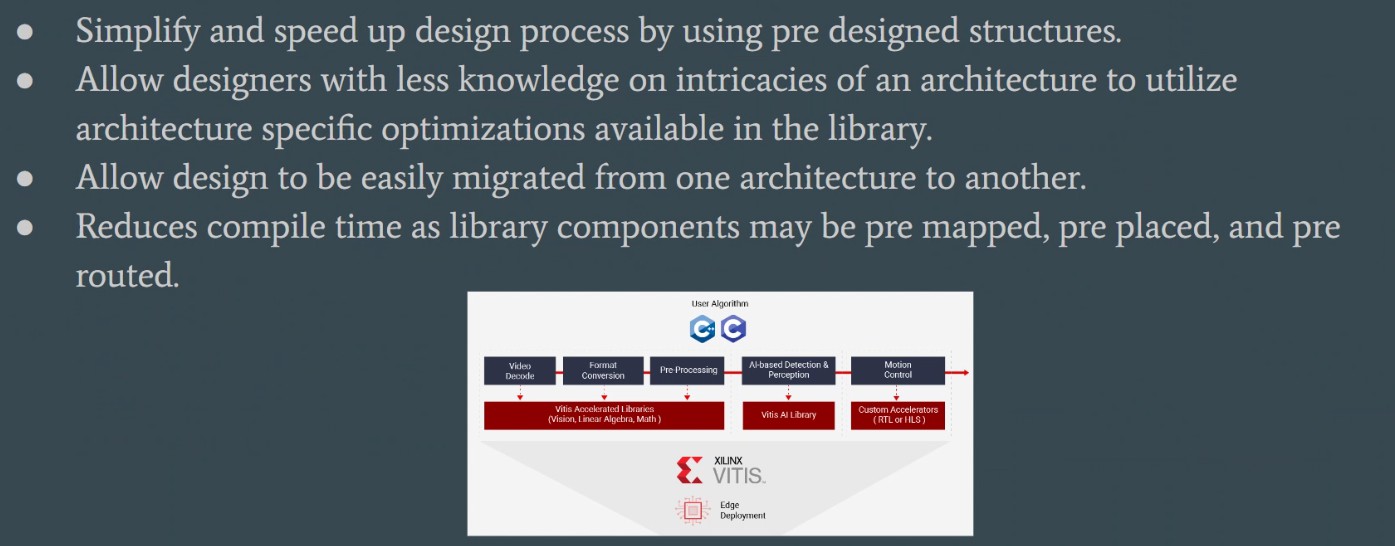

Circuit Libraries

Circuit Generators

Other Compiler Functionalities

- Partial evaluation

- Memory allocation

- Parallelisation

Design Patterns

We want to balance area cost and latency

- Datapath Serialisation

- Hardware / Software partitioning

- Coarse-grain time multiplexing

Efficient Hardware Reuse

- Pipelining

- Retiming

- C-Slow

C-Slow

Use n registers and spreading them around, reducing critical path

Hardware Specialisation

Use hardware bitlevel optimisations

- Instance generator

- Constructors

- Template

Value Added Memory

- Read-Modify-Write cycle

- Scan-Select-Reorganise

- Content-Addressable memory (index is equal to the value?)