VHDL Tricks

Contents

VHDL Packages

Entities

Generics

Entities can have properties which can be set by the implementation during instantiation.

| |

If an assignment requires the length of a generic, we can use the OTHERS keyword as a wildcard. (Refer to $n$-bit registers)

To set these values during instantiation, we use the GENERIC MAP declaration.

| |

Buffer Ports

Apart from the IN and OUT modes of a port, a port can also have a BUFFER mode - which allows for reading and writing from and to that port.

Multiplexing with SELECT

Note: Evaluation of all cases is done concurrently

- f <- w0 when S = 0, else w1

| |

- 4-to-1 (2bit)

| |

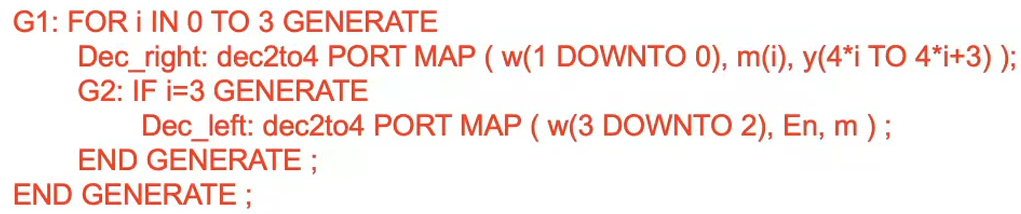

Generation Statements

Shorthand to instantiate multiple components where they only differ by one variable. (i.e. multiple muxers which folow a pattern)

| |

Conditional Generation with IF

Conditional Assignment with WHEN ... ELSE

| |

- Can also combine multiple cases

- Note: They are evaluated sequentially in order (left to right)

| |

Concatenation using &

Can define a signal with a length as the sum of two other signal lengths

| |

Processes

Statements are executed sequentially.

A process listens to a "sensitivity list", and only triggers when a value inside the sensitivity list updates. Only variables that are used in a condition or assignment should appear in a sensitivity list

| |

- Assignments are committed at the end of the process

NOTE: Processes that describe combination logic (circuits without memory) MUST assign a value to every output signal for every execution path

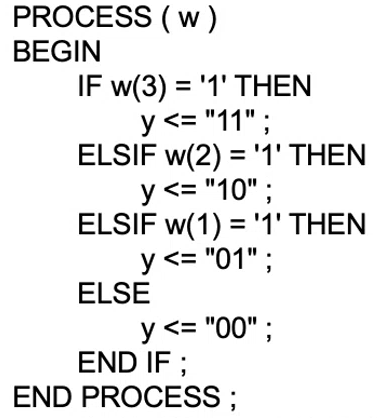

IF ... THEN ... ELSIF ... THEN ... ELSE ... END IF

IF statements can be used inside a PROCESS

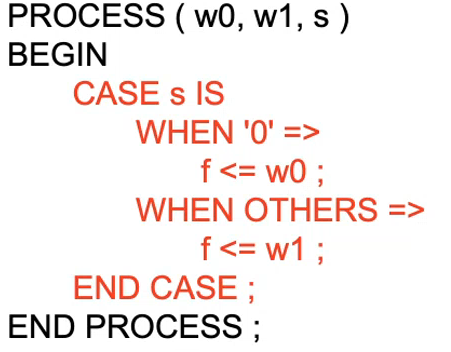

CASE

FOR ... LOOP

| |

WAIT UNTIL

Makes the process always run, but only continues when a condition is true

| |

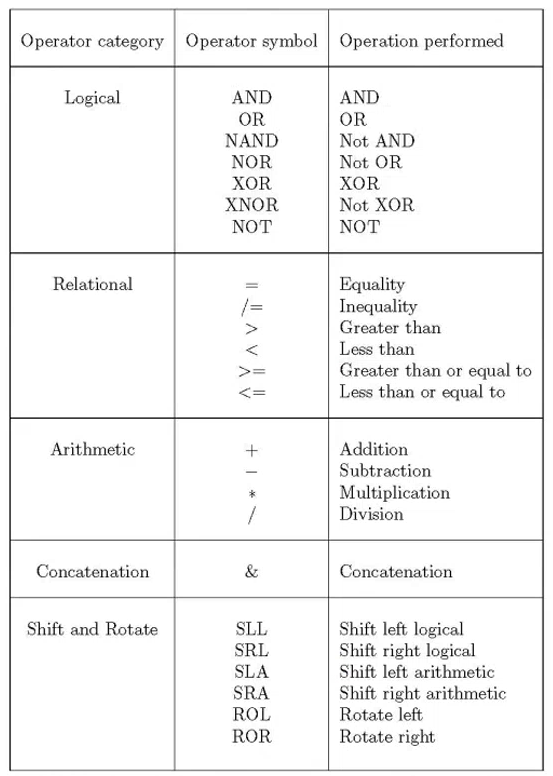

Operators