Synchronous Circuits

Contents

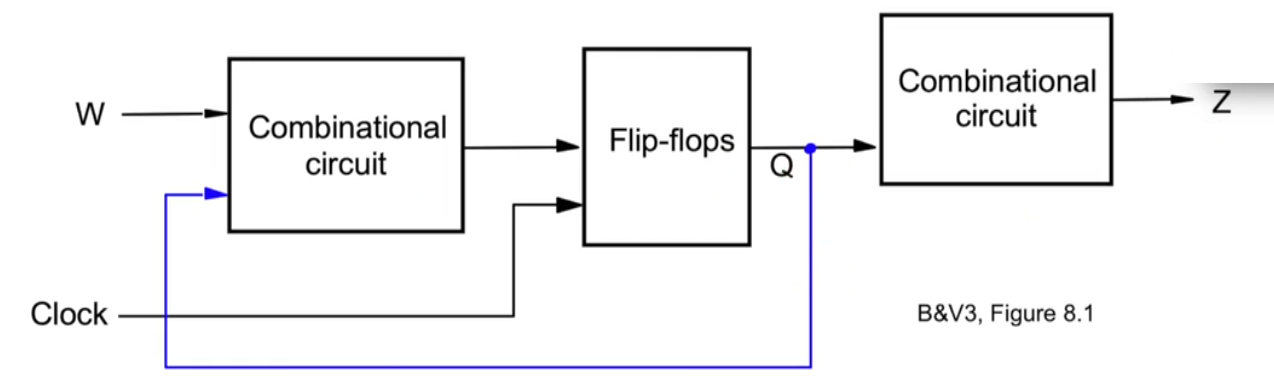

Sequential Circuits

- Outputs depend on past inputs and states, as well as present inputs

- Sequential circuits which use clock signals are known as synchronous sequential circuits

Synchronous Sequential Circuits

- Also known as finite state machines

W- inputQ- present state

A circuit is said to be a Moore type circuit if the output state only depends on the current state Q

A circuit is said to be a Mealy type circuit if the output state depends on the current state Q, and the input W - Uses less states!

Note: Transitions only occur on the NEXT clock edge cycle

Design

- The first step is to determine the number of states in a system

- Assume we start on a reset state

- Find the possible next states

- Find the possible next states

- ...

- Find the possible next states

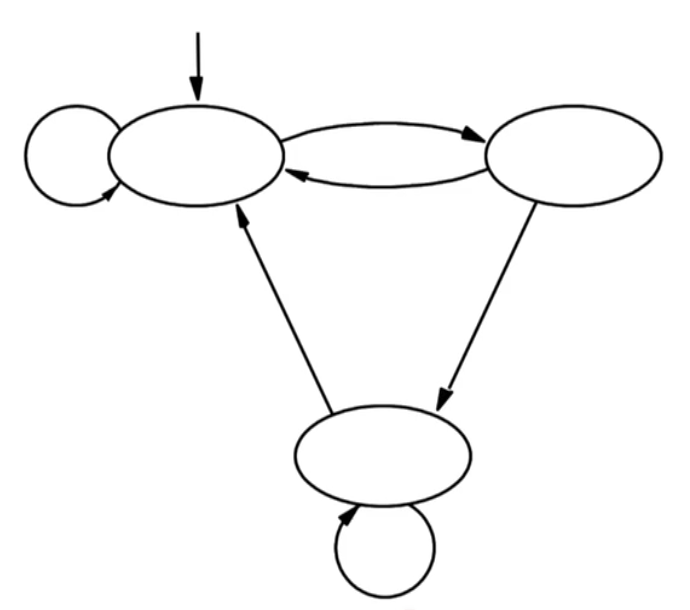

- Create state diagram

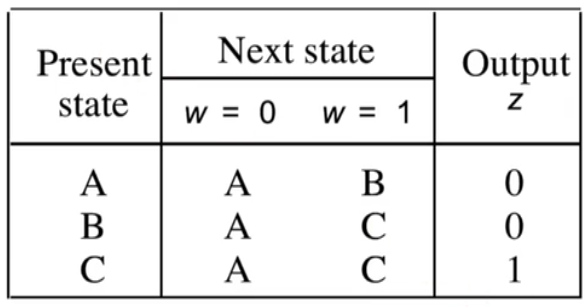

- Create state table

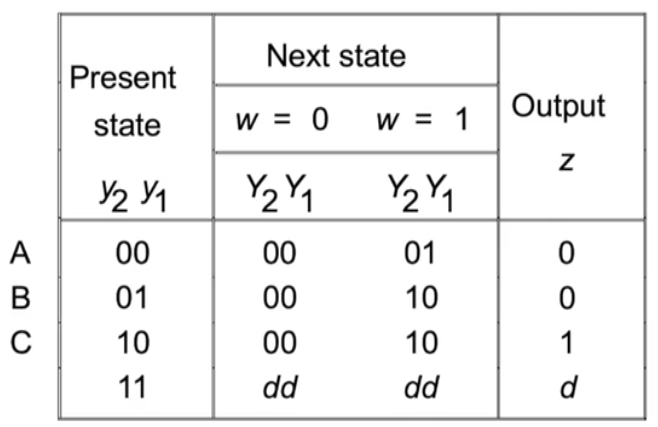

- Create state assignment table

- Derive state logic expression

State Diagram

- Transitions of a Moore type circuit are labelled with the state condition

- Transitions of a Mealy type circuit are labelled with both the state condition and input value

State Table

State Assignment

States can be implemented through variables (flip-flops)

A Karnaugh map can be used to map states from a state-assigned table

CAD tooling for FSMs

- Enumerated type -

TYPE State_type IS (A, B, C); - Define a signal of state type,

SIGNAL y: State_type; - Use a process (sensitive to clock) that switches on

ywithCASE

A more common way

- Create two signals

y_presentandy_next - Use a process (sensitive to clock, and executes on clock edge) that sets

y_present <= y_next; z <= '1' WHEN y_present = C ELSE '0'

Aside: Overriding state values

| |

Aside: If you don't want to use ENUM

- Define each state as a logic vector with a value

- Requires a

WHEN OTHERS =>clause

Async inputs on a Mealy machine

The output should not be asserted until after the input is asserted for 1 clock period

Register Swapping

Mealy circuit can swap two registers one clock cycle quicker (3) opposed to the Moore type circuit (4 cycles)

State Minimisation

Equivalent - Two states are equivalent if they have the same output for every input sequence

- A good state assignment is more important than state minimisation to obtain a low-cost implementation