Counters

Contents

Counters

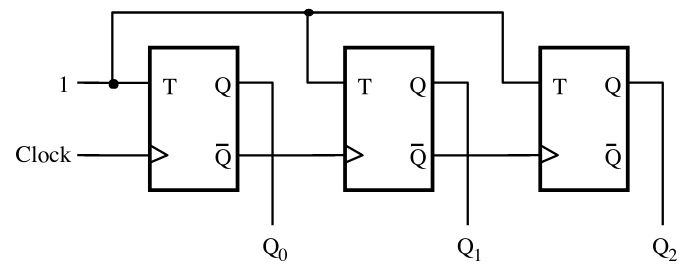

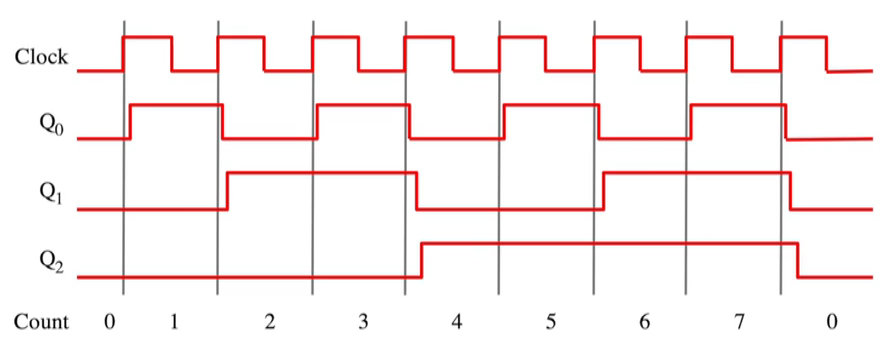

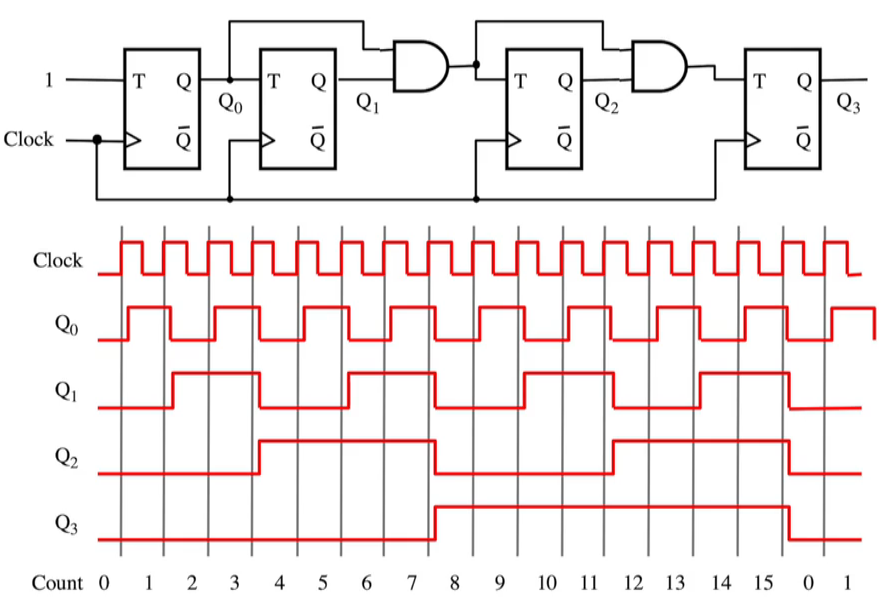

Counters operate by taking the output of a flip-flop as its clock input

| Circuit | Table |

|---|---|

|  |

Note: As a result of propagation delay, there is some time rippling that occurs. This causes some glitching (between count 3 and 4 there are four different values).

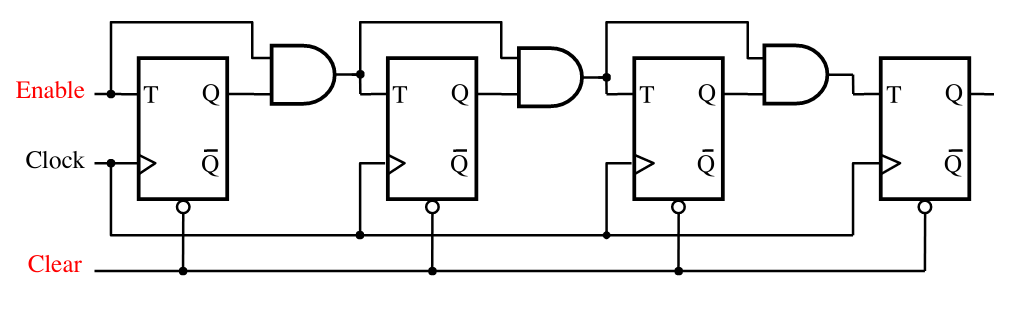

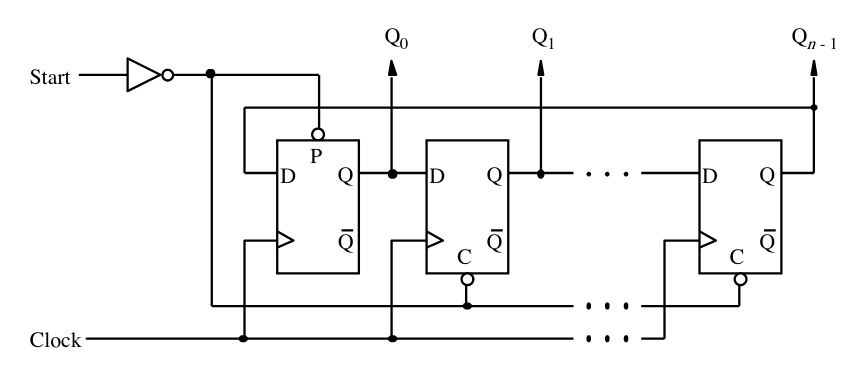

Solution

- Use the same clock signal for all circuits

- Only trigger the flip-flop when pre-requisites are met (i.e. 0b011 become 0b100)

- i.e. AND gate the input with previous conditions

Note: Clock time >= Critical Path

Critical Path: Propagation delay ($t_{cQ}$) + delay(AND gates) + $t_{su}$

Asynchronous Enable and Clear

Synchronous Enable

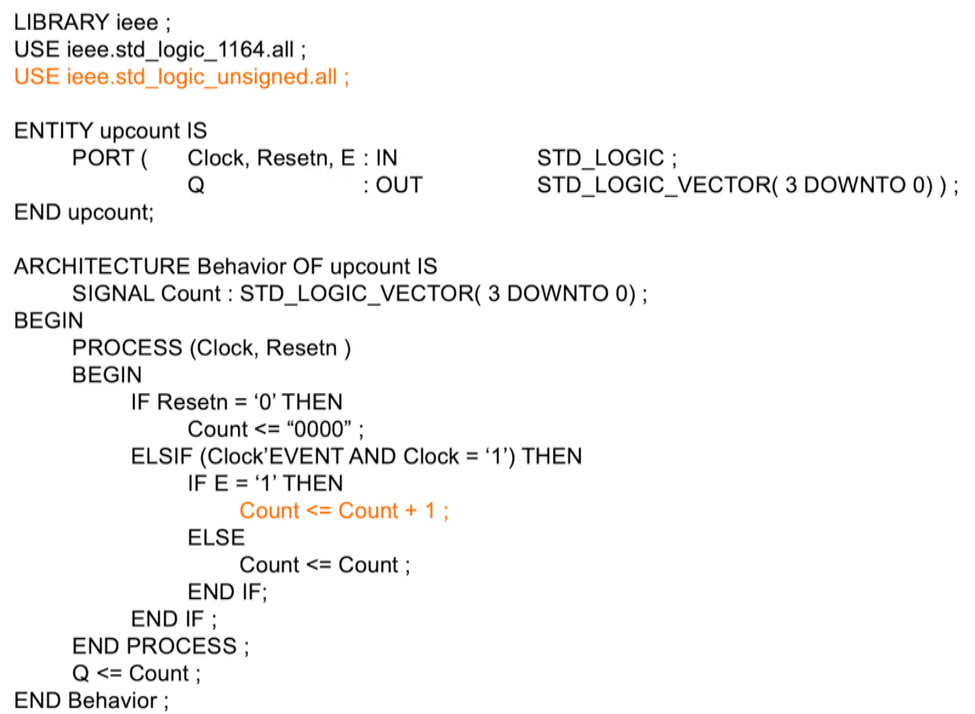

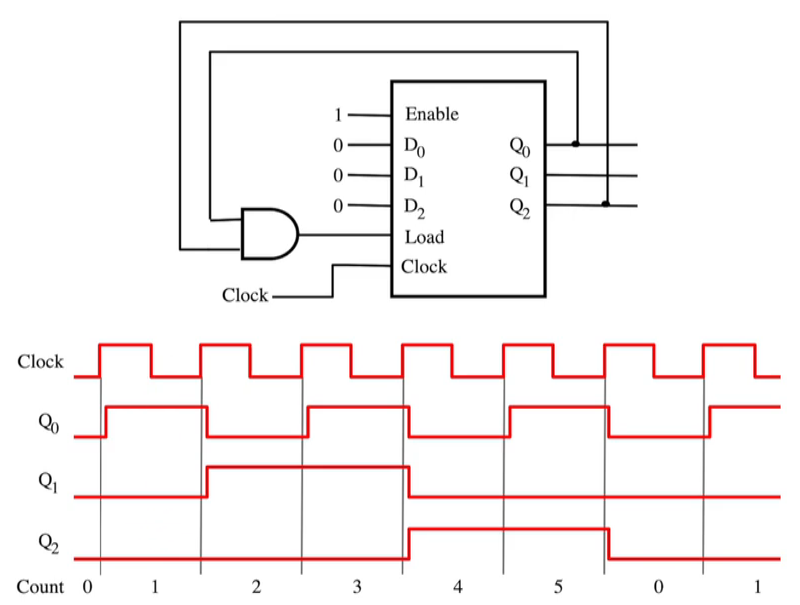

Behaviourial Code

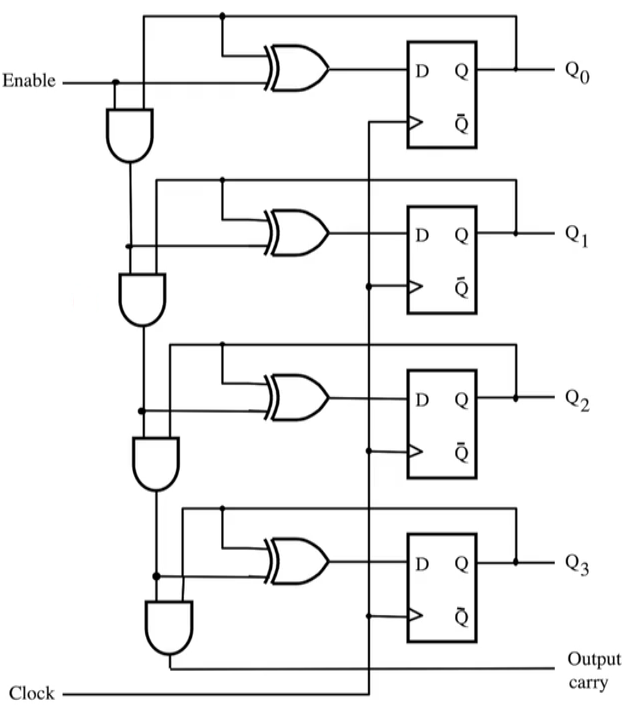

Starting the counter from any value

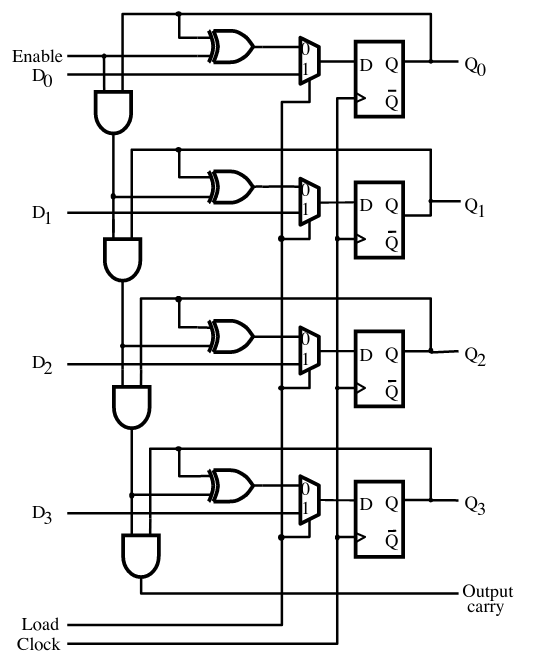

Parallel loading with an input signal, and load flag

| Circuit | Similar Code |

|---|---|

|  |

Note: Code doesn't include the load flag

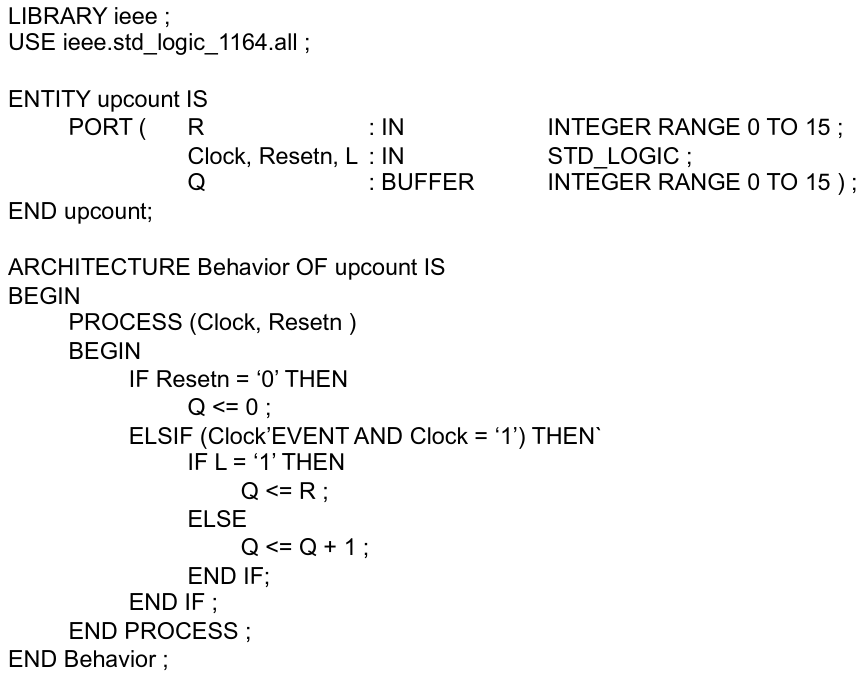

Modulo Counter

For counters that do not use the max range of values ($2^n$) of an $n$-bit signal, we can use a loading circuit that gets triggered on a certain state

i.e Modulo 6 Counter

When Q = 5, perform a load of 0 during the next cycle.

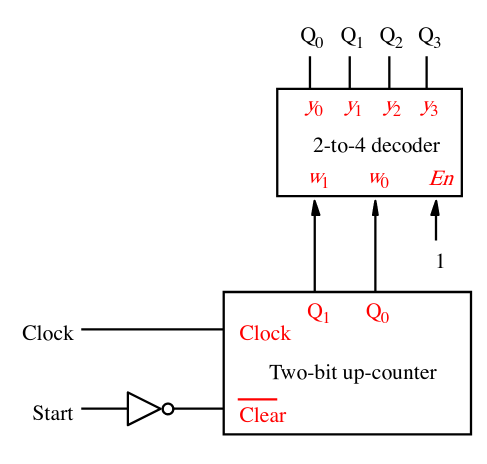

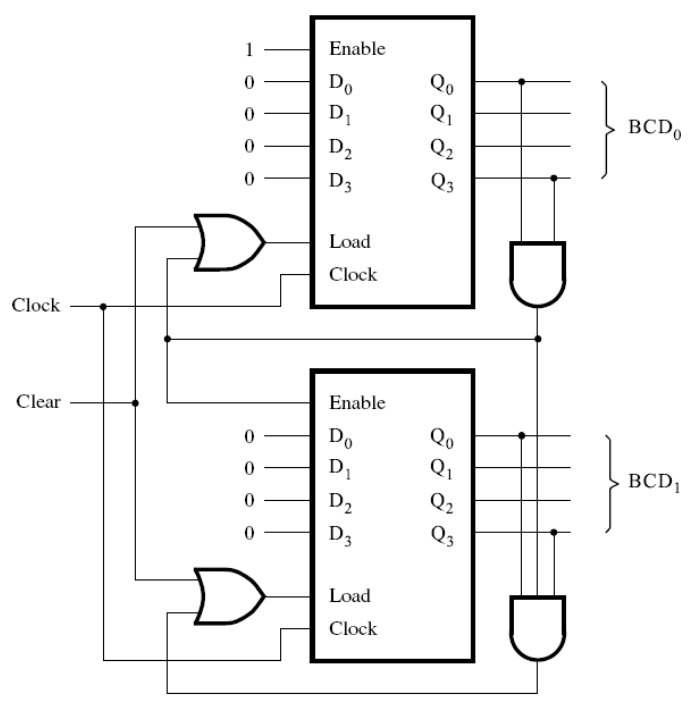

Two Digit Counter

Ring Counter

Alternative